随着芯片不断向微型化发展,工艺制程开始向着更小的5nm、3nm推进,已经_香港回收芯片_越来越逼近物理极限,

2021/5/12 11:43:10 点击:598

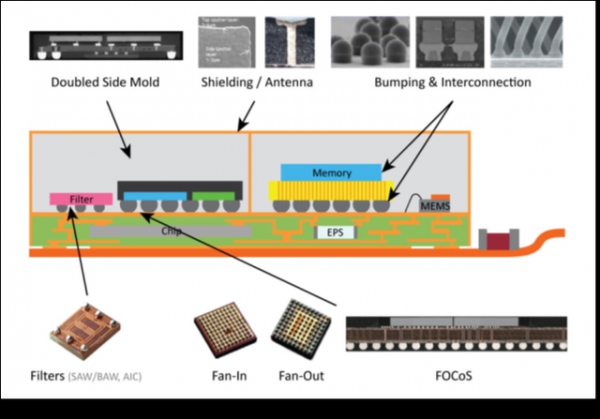

近年来,封装技术在半导体领域发挥的作用越来越大,越来越多前道工艺需要完成的步骤被引入后道工艺当中,两者的界限变得越来越模糊。随之而来的是,越来越多超越传统封装理念的先进封装技术被提出。

满足芯片发展需求需要先进封装

付出的代价也将越来越大,因此摩尔定律屡屡被传将走到尽头,迫切需要另辟蹊径推动技术进步。

先进封装会成为下一阶段AD825AR半导体技术的重要发展方向。随着摩尔定律发展趋缓,通过先进封装技术来满足系统微型化、多功能化成为了集成电路产业发展的新引擎。

先进封装技术能够相对轻松地实现芯片的高密度集成、体积的微型化和更低的成本等需求,符合高端芯片向尺寸更小、性能更高、功耗更低演进的趋势。

如今AI市场的不断扩张推动着先进封装行业的增长,AI芯片组需要运算速度更快的内核、更小巧的外形以及高能效,这些需求驱动着先进封装市场。

5G技术的普及也在增加先进封装市场的需求,5G芯片组较依赖先进封装技术,来实现高性能、小尺寸和低功耗。

先进封装市场将从当前市场价值升至到超过250亿美元,到2026年将超过400亿美元,2020年到2026年期间将是增长的高爆期,其年复合增长率将达到8%。

2.png

异构整合:治疗芯片微缩难题

半导体先进制程纷纷迈入了7纳米、5纳米,接着开始朝3纳米和2纳米迈进,电晶体大小也因此不断接近原子的物理体积限制,电子及物理的限制也让先进制程的持续微缩与升级难度越来越高。

异构整合概念便应运而生,同时成为IC芯片的创新动能。将两种不同制程、不同性质的芯片整合在一起。

这增强了功能性,可以对采用不同工艺、不同功能、不同制造商制造的组件进行封装。

因此,IC代工、制造及半导体设备业者纷纷投入异构整合发展,2.5D、3D封装、Chiplets等现今热门的封装技术,便是基于异构整合的想法。

3.png

2.5D封装:治疗芯片生产成本难题

随着智能手机、AIoT等应用,不仅需要更高的性能,还要保持小体积、低功耗。

在这样的情况下,必须想办法将更多的芯片堆积起来使体积再缩小,因此目前封装技术除了原有的SiP之外,也纷纷朝向立体封装技术发展,2.5D封装技术正是其中被人所熟知的一种。

2.5D封装通常用于ASIC、FPGA、GPU和内存立方体,并最终在高带宽内存(HBM)处理器集成中流行起来。

扇出型晶圆级封装(FOWLP)也可归为2.5D封装的一种方式。扇出型晶圆级封装技术的原理,是从半导体裸晶的端点上,拉出需要的电路至重分布层,进而形成封装。

扇出型晶圆级封装为晶圆模提供了更多的外部接触空间,将芯片嵌入环氧模塑料内,然后在晶片表面制造高密度重分布层(RDL)和焊料球,形成重组晶片。

3D封装技术:直接将芯片堆叠起来

在3DIC封装中,逻辑模块堆叠在内存模块上,而不是创建一个大型的系统片上(SoC),并且模块通过一个主动交互器连接。

相较于2.5D封装,3D封装的原理是在芯片制作电晶体(CMOS)结构,并且直接使用硅穿孔来连结上下不同芯片的电子讯号,以直接将记忆体或其他芯片垂直堆叠在上面。

此项封装最大的技术挑战便是,要在芯片内直接制作硅穿孔困难度极高,不过,由于高效能运算、人工智能等应用兴起,加上硅通孔(TSV)技术愈来愈成熟,可以看到越来越多的CPU、GPU和记忆体开始采用3D封装。

Chiplets:摩尔定律瓶颈衍生的技术替代方案

由于电子终端产品朝向高整合趋势发展,对于高效能芯片需求持续增加,但随着摩尔定律逐渐趋缓,在持续提升产品性能过程中,如果为了整合新功能芯片模组而增大芯片面积,将会面临成本提高和低良率问题。

因此,Chiplets成为半导体产业因摩尔定律面临瓶颈所衍生的技术替代方案。

因为先进制程成本非常高昂,特别是模拟电路、I/O等愈来愈难以随着制程技术缩小,而Chiplets是将电路分割成独立的小芯片,并各自强化功能、制程技术及尺寸,最后整合在一起,以克服制程难以微缩的挑战。

Chiplets允许设计者利用各种各样的IP而不必考虑它们是在哪个节点或技术上制造;它们可以在硅、玻璃和层压板等多种材料上建造。

芯片巨头同时深入探索封装技术

以台积电、英特尔、三星为代表的三大芯片巨头正积极探索先进封装技术。

台积电:

·CoWoS是台积电推出的2.5D封装技术,被称为晶圆级封装,CoWoS针对高端市场,连线数量和封装尺寸都比较大。

自2012年开始量产CoWoS以来,台积电就通过这种芯片间共享基板的封装形式,把多颗芯片封装到一起,而平面上的裸片通过SiliconInterposer互联,这样达到了封装体积小,传输速度高,功耗低,引脚少的效果。

·开发了晶圆级封装技术——系统整合芯片,是以关键的铜到铜接合结构,搭配TSV以实现最先进的3D IC技术,可将多个小芯片整合成一个面积更小与轮廓更薄的系统单晶片。

·在Fan-out和3D先进封装平台方面已处于领先地位,其先进封装技术俨然已成为一项成熟的业务,并为其带来了可观的收入。

目前有4座先进的芯片封测工厂,新投产两座之后,就将增加到6座,在明后两年投产的两座芯片封装工厂,也将采用3D Fabric先进封装技术。

·台积电将SoIC、CoWoS、InFO-R、CoW、WoW等先进封装技术平台加以整合,统一命名为“TSMC 3D Fabric”。

此平台将提供芯片连接解决方案,满足用户在整合数字芯片、高带宽存储芯片及特殊工艺芯片方面的需求。

三星:

·主要布局在面板级扇出型封装(FOPLP),三星在FOPLP投资已超过4亿美元。2018年FOPLP技术实现商用,应用于其自家智能手手表Galaxy Watch的处理器封装应用中。

·为扩大半导体封装技术阵容,不仅开发FOPLP,也开发FOWLP技术。还在2019年上半年收购子公司三星电机的半导体封装PLP事业,不断加强封装的实力。

·2019年10月,三星开发出业界首个12层3D-TSV(硅穿孔)技术,这项新创新被认为是大规模生产高性能芯片所面临的的最具挑战性的封装技术之一,因为它需要极高的精度才能通过拥有六万多个TSV孔的三维配置垂直互连12个DRAM芯片。

英特尔:

·2017年,英特尔推出了EMIB(嵌入式多芯片互连桥接)封装技术,可将不同类型、不同工艺的芯片IP灵活地组合在一起,类似一个松散的SoC。

·随后发布了3D封装技术Foveros,首次在逻辑芯片中实现3D堆叠,对不同种类芯片进行异构集成。

英特尔的3D封装技术结合了3D和2D堆叠的两项优势,英特尔ODI全向互连技术可通过在小芯片之间的布线空隙来实现,而这些是台积电系统整合单晶片(So IC)技术做不到的。

·最新发布的“混合结合”技术,能够实现10微米及以下的凸点间距,较Fovreros封装的25—50微米凸点间距有了明显提升,并且优化芯片的互连密度、带宽和功率表现,进一步提升芯片系统的计算效能。

- 上一篇:就现阶段,国内半导体真的尚缺乏实力与条件,加强芯片先进_香港封装芯片报废销毁处理_封装技术是才是他们应该干的! 2021/5/12

- 下一篇:半导体封装设备和锂电池设备领域_香港回收半导体_的大佬都有谁? 2021/5/12